# Driving High-Level Loads With Optocouplers (Appnote 4)

Frequently a load to be driven by an optocoupler requires more current, voltage, or both, than an optocoupler can provide at its output.

Available optocoupler output current is found by multiplying input (LED section) current by the "CTR" or current transfer ratio. For worst-case design, the minimum specified value would be used. The minimum CTR of the IL1 is 20 %. Temperature derating is not usually necessary over the 0 °C to + 60 °C range because the LED light output and transistor beta have approximately compensating coefficients.

Multiplying the minimum CTR by 0.9 would ensure a safe design over this temperature range. Over a wide range, more margin would be required.

The LED source current is limited by its rated power dissipation. Table 1 shows maximum allowable  $I_F$  versus maximum ambient temperature.

Values for Table 1 are based on a 1.33 mW/°C derate from the 100 mW at 25 °C power rating.

| Maximum Temperature | I <sub>F</sub> Maximum |

|---------------------|------------------------|

| 40°C                | 50 mA                  |

| 60°C                | 35 mA                  |

| 80°C                | 17 mA                  |

Table 1:

Obviously, one can increase the available output current either by choosing a higher CTR-rated optocoupler or by providing more current, or both. Table 2 shows the minimum available output current for the IL1, at  $T_A = 60\,^{\circ}\text{C}$  (from Table 1) and a 10 percent margin for temperature effects.

| P/N | I <sub>CE</sub> (min) mA |

|-----|--------------------------|

| IL1 | 6.3                      |

Table 2:

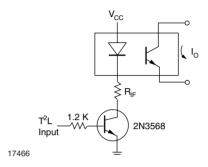

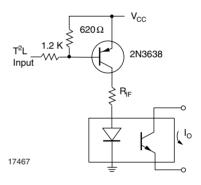

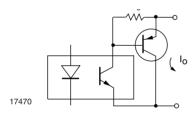

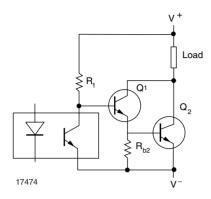

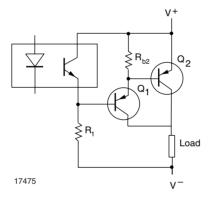

If the IL1 is being operated from logic with 5 V driving transistor and 0.2 V  $V_{CE}$  saturation is assumed for the driving transistor; a 75  $\Omega$   $R_{IF}$  resistor will provide the 48 mA. The forward voltage of the IR-emitting LED is about 1.2 V. Figures 1 and Figure 2 show two such drive circuits.

Figure 1. NPN driver

Figure 2. PNP driver

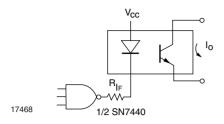

A "buffer-gate," such as the SN7440 provides a very good alternative to discrete transistor drivers. Figure 3 shows how this is done. Note that the gate is used in the "current-sinking" rather than the "current-sourcing" mode. In other words, conventional current flows into the buffer-gate to turn on the LED. This makes use of the fact that a  $\rm T^2L$  gate will sink more current than it will source. The SN7440 is specified to drive thirty 1.6 mA loads or 48 mA. Changing  $\rm R_{IF}$  from 75 to 68  $\Omega$  adjusts for the higher saturation voltage of the monolithic device.

## **Vishay Semiconductors**

Figure 3. Buffer-gate drive

#### **More Current**

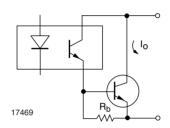

For load currents greater than 6.3 mA, a current amplifier is required. Figure 4 and Figure 5 show two simple one-transistor current amplifier circuits.

Figure 4. NPN current booster

Figure 5. PNP current booster

Since the transistor in the optocoupler is treated as a two-terminal device, no operational difference exists between the NPN and the PNP circuits. R<sub>b</sub> provides a return path for I<sub>CBO</sub> of the output transistor. Its value is:  $R_b = 400 \text{ mV/I}_{CBO}$  (T) where  $I_{CBO}$ (T) is found for the highest junction temperature expected.

Assume that leakage currents double every ten degrees. Use the maximum dissipated power, the specified maximum junction-to-ambient thermal resistance, and the maximum design ambient temperature in conjunction with the specified maximum 25°  $I_{CBO}$ to calculate I<sub>CBO</sub>(T).As an example, suppose a 2N3568 is used to provide a 100 mA load current. Also assume a maximum steady-state transistor power dissipation of 100 mW and a 60°C maximum ambient. The transistor junction-to-ambient thermal resistance is 333° C/watt, so a maximum junction temperature of 60 + 33 or 93 °C is expected. This is about 7 decades above 25 °C.

Therefore,

$I_{CBO}(T) = I_{CBO}(max) \times 27 = 50 \text{ nA} \times 128 = 6.5 \mu A.$ A safe value for  $R_h$  is 400 mV/6.5  $\mu A = 62 \text{ k}\Omega$ .

Working backwards, maximum base current under load will be  $I_O/h_{FF}(min) = 100 \text{ mA}/100 = 1 \text{ mA}$ . Current in  $R_b$  is  $V_{BE}/R_b = 600$  mV/60 k = 10  $\mu$ A, which is negligible. An IL1 with a 9 mA drive would operate effectively.

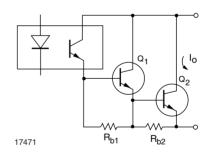

If the load requires more current than can be obtained with the highest beta transistor available, then more than one transistor must be used in cascade. For example, suppose 3 A load current and 10 W dissipation are needed. A Motorola MJE3055 might be used for the output transistor, driven by a MJE205 as shown in Figure 6. Using a 5 °/W heat sink and the rated MJE3055 junction-to-case thermal resistance of 1.4 °/W, we find that junction temperature rise is 6.4 x 10, or 64 °. Therefore maximum junction temperature is 124 °C. This is 10 decades above 25 °C making  $I_{CBO}(T) = 2^{10} I_{CBO}(max) = 10^3 I_{CBO}(max)$ I<sub>CBO</sub>(max) at 30 V or less is not given, but I<sub>CEO</sub> is. Using (for safety) a value of 20 for the minimum low current h<sub>FE</sub> of the device, l<sub>CBO</sub> could be as large as  $I_{CEO}/20 = 35 \mu A$ . Then  $I_{CBO}(T)$  is 35 mA and  $R_{b2} = 400 \text{ mV}/35 \text{ mA} = 11 \Omega$ . For  $I_b$  use  $I_0/h_{FF}$ (min. at 4 A) = 3 A/20 = 150 mA.

$I_{Rb2} = 600 \text{ mV} / 10 \Omega = 60 \text{ mA}, \text{ so } I_{e(Q1)} = 210 \text{ mA}$

Figure 6. Two NPN current boosters

Maximum power in Q<sub>1</sub> will be about 1/14 the power in Q<sub>2</sub> since its current is lower by that ratio and the two collector-to-emitter voltages are nearly the same. This means Q<sub>1</sub> must dissipate 700 mW.

Assuming a small "flag" heat sink having 50°/W thermal resistance, we find the junction at about 95°C. The 150 °C case temperature I<sub>CBO</sub> rating for this device is 2 mA, so one can work backwards and

assume about 1/30 of this value, or 70 µA. On the other hand, the 25° rated I<sub>CBO</sub> is 100 µA. Choosing the larger of these contradictory specifications.

$R_{b1}$  = 400 mV/0.1 mA = 4 k  $\approx$  3.9 k.  $Q_1$  base current is  $I_{E(Q1)}/h_{FE(Q1-mjn)} = 210 \text{ mA/}50^* = 4.2 \text{ mA}$ . Total current is  $I_{b(Q1)} + I_{Rb1} = 4.2 + 0.24 = 4.5$  mA. Table 2 shows that an IL1 could be used here.

Minimum h<sub>FE</sub> is obtained using the specification at I<sub>CF</sub> = 2 A and the "Normalized DC Current Gain" graph given in Motorola's "Semiconductor Data Book", 5th edition, pp. 7-232 and 7-233.

#### **More Load Voltages**

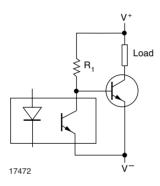

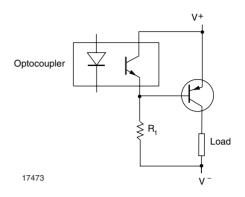

All of the current-gain circuits shown so far have one common feature: load voltage is limited by the 30 V rating of the IL1 not by the voltage or power rating of the transistor(s).

Figure 7 shows a method of overcoming this limitation. This circuit will stand off BV<sub>CEO</sub> of Q<sub>1</sub>. The voltage rating of the phototransistor is irrelevant since its maximum collector-emitter voltage is the base emitter voltage of Q<sub>1</sub> (about 0.7 V).

Figure 7. NPN HV booster

Figure 8. PNP HV booster

Unlike the "Darlington" configurations shown previously, this circuit operates "normally-ON." When no current flows in the LED the phototransistor, being OFF, allows R<sub>2</sub> current to flow into the base of Q<sub>1</sub>, turning Q<sub>1</sub> ON. When the optocoupler is energized, its phototransistor "shorts out" the R2 current turning Q1 OFF.

The value of R<sub>1</sub> depends only on the load-supply voltage V<sup>+</sup> – V<sup>-</sup>, and the maximum required Q<sub>1</sub> base current. This is derived from the minimum beta Of Q1 at minimum temperature and the load current. The required current-drive capability is the same as IR1, since I<sub>R1</sub> changes negligibly when the circuit goes between its "ON" and "OFF" states.

In some applications either more current gain will be required than one transistor can provide or the power dissipated in R<sub>1</sub> will be objectionable. In these cases, simply use the Darlington high-voltage boosters shown in Figure 9.

If more than one load is being driven and their negative terminals must be in common, use the PNP circuit (Figure 10). Otherwise, the NPN is better because the transistors cost less. Performance characteristics of the NPN and PNP versions are identical if the device parameters are also the same.

Document Number: 83704 www.vishay.com

## **Vishay Semiconductors**

Figure 9. NPN Darlington HV booster

Figure 10. PNP Darlington HV booster

#### **Applications**

Optocoupler isolated circuits are useful wherever ground loop problems exist in systems, or where dc voltage level translations are needed. In many systems so-called interpose relays are used between a logic circuit section (which may be a mini-computer) and the devices being controlled. Sometimes *two levels* of interpose relays are used in cascade either because of the load power level or because of extreme difficulties with EMI. Optocouplers aided by booster circuits such as those described can replace many of the relays in these systems.

The reed relays, typically used as the first level of interpose and mounted on the interface logic cards in the electronic part of the system, are almost always replaceable by optocouplers since their load is just the coil of a larger relay. This relay may have a coil power of 1/2 to 5 W and operate on 12, 24 or 48 V dc. Assuming worst-case design techniques are carefully followed, system reliability should improve in proportion to the number of relays replaced.

www.vishay.com

Document Number: 83704

Revision 1.3, 24-Nov-03